# QORVO PROFESSIONAL TRAINING

ANALOG & MIXED-MODE SIGNAL IC LAYOUT DESIGN

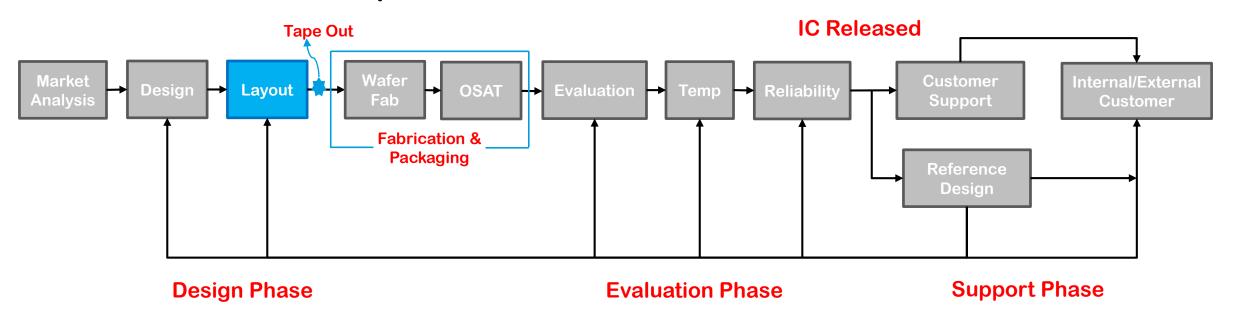

## Research & Development IC - Full Flow

#### **Design Phase**

# Mixed Mode Signal Design

\*\*Analog Design Engineer

\*\*Digital Design Engineer

& Customer

#### **Layout Design**

\*\*Layout Design Engineer

\*\*Digital Design Engineer

& Analog Design Engineer

#### **Evaluation Phase**

#### **Evaluation**

\*\*Application/Firmware

Engineer

& Analog Design Engineer

& Digital Design Engineer

**Temp - Realiability**

\*\*Test Development Engineer

\*\*Production Engineer

& Analog Design Engineer

## What does Layout Design Engineer do?

- ✓ Transform circuits diagrams into physical layouts using Cadence Virtuoso Layout Suite, ensure components are accurately placed and connected on the semiconductor chip

- ✓ Optimize circuit layout designs for various parameters like area, power consumption, signal integrity and overall circuit performance

- ✓ Verify layout (LVS, DRC,...) with modern tools to ensure production capacity according to the requirements of the microchip factory.

- ✓ Identify and troubleshooting layout related problems, implement solution to meet design specification & requirement

- ✓ Perform floor-planning so that the microchip can be bonded to the package.

- ✓ Write additional rule-decks to automate the layout optimization process so that the chip achieves the best results, with the fewest unwanted parasitic components.

What you should do to be come a Layout Design Engineer: Qorvo professional training course for IC Layout design!

#### Fundamental Knowledge:

- **Electronic Circuit Theory**

- > Electronic Components

#### Advanced Knowledge:

- ❖ Books:

- IC Layout Basics (by Christopher Saint, Judy Saint)

- The Art of Analog Layout (by Alan Hastings)

- **❖ Tools: Cadence, Mentor Graphics**

- ❖ Forum: <a href="https://www.edaboard.com/forums/analog-integrated-circuit-ic-design-layout-and.39/">https://www.edaboard.com/forums/analog-integrated-circuit-ic-design-layout-and.39/</a>

# Agenda

- 1. Objectives & Target Outcomes

- 2. Training Modules

- 3. Course Outlines

- 4. Books & Reference Source

# 1. Objectives & Target Outcomes

### **Analog & Mixed-Mode Signal IC Layout Design**

#### **OBJECTIVES**

- √Training duration: 12 weeks.

- ✓ Integrate theory and practice.

- ✓ Acquire fundamental and essential knowledge of Analog and Mixed-mode signal IC layout design.

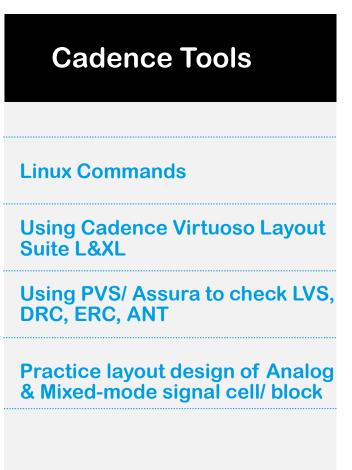

- ✓ Gain proficiency in using industry-standard IC layout design tools: Cadence Virtuoso.

- ✓ Learn to adhere to design rules, constraints and specifications in IC layout.

- ✓ Create a portfolio showcasing layout projects and demonstrate proficiency in semiconductor-relevant skills

- ✓ Cultivate a mindset for ongoing learning and staying updated with industry trends and advancement in IC layout design

#### **TARGET OUTCOMES**

- ➤ Efficient Design Practices: Implement layout designs that optimize area, power and performance metrics for cell and block level.

- Produce Design Tools: Be able to use Cadence Virtuoso Layout Suite L/XL.

- Debug: Develop ability to troubleshoot and debug layout-related issues effectively, capable in using PVS/ Calibre/ Assura to verify layout and fix bugs.

- Cross-functional collaboration: Demonstrate effective communication and collaboration with team members from diverse disciplines

- Documentation Proficiency: Maintain thorough and well-organized documentation for all layout designs.

# 2. Training Modules

## **Analog & Mixed-Mode Signal IC Layout Design**

| IC Fabrication Flow           | Components | Device Matching            |

|-------------------------------|------------|----------------------------|

| Introduction analog IC design | MOSFET     | Why need matching?         |

| Basic steps of IC fabrication | BJT        | Typical matching methods   |

| EDA tool introduction         | Resistor   | Bi-CMOS matching example   |

|                               | Capacitor  | Resistor matching example  |

|                               | Diode      | Capacitor matching example |

# 2. Training Modules

### **Analog & Mixed-Mode Signal IC Layout Design**

| Basic Steps of Layout Design |

|------------------------------|

| Device generation            |

| Floor planning               |

| Placement                    |

| Routing                      |

|                              |

## 3. Course Outlines

#### **Analog & Mixed-Mode Signal IC Layout Design**

## Scope of Knowledge and IC Layout Design Practices

| Week                                       | Theory                                                                                                                                                         | Hands-on/ Practice                                                            |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Week 1:<br>Introduction                    | Basic theory: IC fabrication, introduction analog IC design, EDA tools                                                                                         |                                                                               |

| Week 2:<br>Components                      | <ul> <li>Resistor, Capacitor, CMOS,<br/>Diode and Bipolar.</li> <li>Approaching Cadence Virtuoso<br/>Layout Suite L&amp;XL, Cadence<br/>PVS/ Assura</li> </ul> | <ul> <li>Generation device in Cadence<br/>Virtuoso Suite L example</li> </ul> |

| Week 3-4:<br>Device Matching               | <ul><li>Why need matching?</li><li>Type of matching</li></ul>                                                                                                  | <ul> <li>Matching Resistor, Capacitor</li> </ul>                              |

|                                            |                                                                                                                                                                | <ul> <li>Matching CMOS and Bipolar</li> </ul>                                 |

| Week 5:<br>Basic steps of<br>layout Design | Component Placement , Floor Planning, and Routing                                                                                                              |                                                                               |

| Week 6:<br>Layout<br>Verification          | <ul> <li>LVS/DRC Verification with<br/>Assura/PVS tools</li> </ul>                                                                                             | <ul> <li>Using Assura/PVS tools to debug errors</li> </ul>                    |

## Scope of Knowledge and IC Layout Design Practices

| Week                                | Theory                                                                                                                                                                                                                      | Hands-on/ Practice                         |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Week 7:<br>Block Layout             | <ul> <li>Cadence Virtuoso component placement</li> <li>Resistor matching</li> <li>NMOS/PMOS matching</li> <li>BJT matching</li> <li>Capacitor matching</li> <li>Floor Planning</li> <li>Routing</li> <li>LVS/DRC</li> </ul> | <ul> <li>Layout Current mirrors</li> </ul> |

| Week 8:<br>Block Layout             |                                                                                                                                                                                                                             | <ul><li>Layout Resistor DAC</li></ul>      |

| Week 9:<br>Block Layout             |                                                                                                                                                                                                                             | <ul><li>Layout OTA/ Op-Amp</li></ul>       |

| Week 10:<br>Block Layout            |                                                                                                                                                                                                                             | <ul><li>Layout Comparator</li></ul>        |

| Week 11:<br>Block Layout            |                                                                                                                                                                                                                             | ■ Layout a ring Oscillator                 |

| Week 12:<br>Exam &<br>Certification | Hands-on design                                                                                                                                                                                                             | Bandgap Reference block                    |

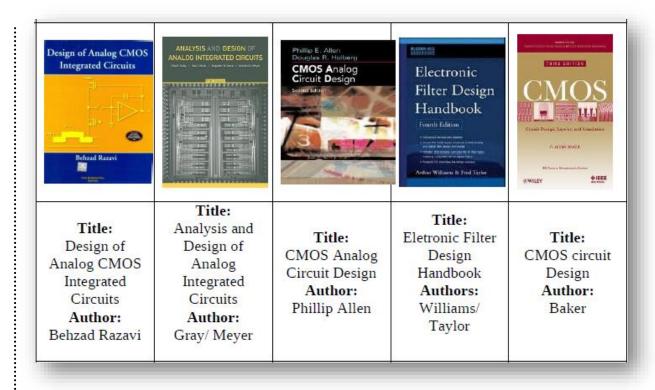

## 4. Books & Reference Sources

- **❖ The Art of Analog Layout** − *Alan Hastings*

- ❖ IC Layout Basics Christopher Saint/ Judy

Saint

- **❖ IC Mask Design** *Christopher Saint*

- Semiconductor Physics and Devices Donald A. Neamen

- **❖ RF Microelectronics** *Behzad Razavi*

- ❖ Thiết kế IC Tương Tự -- Phạm Nguyễn Thanh

Loan